# FPGA Emulation of Quantum Circuits

Ahmed Usman Khalid

Department of Electrical & Computer Engineering McGill University Montreal, Canada

October 2005

A thesis submitted to McGill University in partial fulfilment of the requirements of the degree of Master of Engineering.

$\odot$  2005 Ahmed Usman Khalid

#### Abstract

In recent years, new and novel forms of computation employing different natural phenomena such as the spin of atoms or the orientation of protein molecules have been proposed and are in the very initial stages of development. One of the most promising of these new computation techniques is quantum computing that employs various physical effects observed at the quantum level to provide significant improvement in certain computation tasks such as data search and factorization. An assortment of software-based simulators of quantum computers have been developed recently to assist in the development of this new computation process. However, efficiently simulating quantum algorithms at the software level is quite challenging since the algorithms have exponential run-times and memory requirements. Furthermore, the sequential nature of software-based computation makes simulating the parallel nature of quantum computation exceedingly difficult. In this thesis, the first hardware-based quantum algorithm emulation technique is presented. The emulator uses FPGA technology to model quantum circuits. Parallel computation available at the hardware level allows considerable speed-up as compared to the state-of-the-art software simulators as well as provides a greater insight into precision requirements for simulating quantum circuits.

#### Résumé

Ces dernières annes, de nouvelles techniques innovatrices de computation utilisant divers types de phénomènes naturels tels que la rotation des atomes ou l'orientation des molécules de protéine dans l'espace ont été proposées et sont présentement au stade initial de leur développement. Une technique de computation des plus prometteuses est la computation quantique employant différents effets physiques observés au niveau quantique. Cette technique permet une amélioration significative dans certaines tâches de computation telles que la recherche d'information et la factorisation. Un assortiment de logiciels de simulation d'ordinateur quantique ont récemment été développés pour aider au développement de ce nouveau processus de computation. Cependant, simuler efficacement des algorithmes quantiques au niveau logiciel est une tâche complexe, car ces algorithmes ncessitent une durée d'exécution et des ressources de mémoire exponentielles. De plus, la nature séquentielle de computation sur logiciel rend la simulation de la nature parallèle de la computation quantique extrêmement difficile. Dans cette thèse, le premier émulateur d'algorithme quantique sur hardware est présenté. L'émulateur emploie la technologie FPGA pour modeler des circuits quantiques. La computation parallèle réalisable au niveau hardware permet une accélération considérable du temps d'exécution par rapport aux simulateurs sur logiciels actuels les plus puissants. Également, la technique de simulation sur hardware présente procure plus d'information concernant la précision requise pour simuler des circuits quantiques.

### Acknowledgments

First and foremost, I would like to thank my supervisors Prof. Zeljko Zilic and Prof. Katarzyna Radecka for giving me this opportunity to work with them. This thesis would not have happened if not for their guidance and patience. I would also like to thank the Microelectronics Strategic Alliance of Quebec (ReSMIQ) for their financial support for my research work.

I am also indebted to Jean-Sebastien Chenard for his friendship and guidance throughout my research. He provided invaluable counsel with the synthesis issues of the emulator as well as in the design of the serial communication interface to the PC. I would like to thank Dr. Dmitri Maslov for reviewing the thesis and his comments provided considerable polish to the final draft. I would also like to thank my friends and colleagues in the "Circle of Truth": Sadok Aouini, Simon Hong, Carmen Au, Karthik Sundaresan, Cristian Radita, Dani Tannir and Tarek AlHajj. Their friendship and company made the entire graduate school experience memorable. I would also like to thank Sadok and Cristian for the French translation of the abstract.

Finally, I would like to thank my family. My parents and my brother have been my support throughout my life. However, never have I felt and appreciated their presence more than during my time as a graduate student. Thank you.

# Contents

| 1 | Intr | roduction                                          | 1  |

|---|------|----------------------------------------------------|----|

|   | 1.1  | Quantum Computation vs. Classical Computation      | 2  |

|   | 1.2  | Quantum Circuit Simulation vs. Emulation           | 3  |

|   |      | 1.2.1 Motivation for Emulation of Quantum Circuits | 3  |

|   | 1.3  | Thesis Contribution                                | 4  |

|   | 1.4  | Thesis Organization                                | 4  |

| 2 | Bac  | ckground                                           | 6  |

|   | 2.1  | Quantum Bits                                       | 6  |

|   | 2.2  | Entanglement                                       | 9  |

|   | 2.3  | Quantum Gates                                      | 10 |

|   |      | 2.3.1 Single Input Quantum Gates                   | 10 |

|   |      | 2.3.2 Multiple Input Quantum Gates                 | 12 |

|   | 2.4  | Quantum Measurement                                | 13 |

|   | 2.5  | Quantum Algorithms as Quantum Circuits             | 14 |

|   |      | 2.5.1 Quantum Fourier Transform                    | 14 |

|   |      | 2.5.2 Grover's Search Algorithm                    | 15 |

|   | 2.6  | Software-based Simulation Techniques               | 16 |

|   |      | 2.6.1 QuCalc: Mathematica Simulation Library       | 16 |

|   |      | 2.6.2 QuIDDPro: An ADD based Simulation System     | 17 |

|   |      | 2.6.3 HDL Based Simulation of Quantum Circuits     | 20 |

| 3 | FP   | GA Emulator Design                                 | 22 |

|   | 3.1  | Challenges in Emulating Quantum Circuits           | 22 |

|   | 2.9  | Emulation Overview                                 | 93 |

Contents v

|              | 3.3 | Data primitives                                    | 25 |

|--------------|-----|----------------------------------------------------|----|

|              |     | 3.3.1 Emulation of the expanded state space        | 27 |

|              | 3.4 | Expander Circuits                                  | 28 |

|              |     | 3.4.1 Sequential State Space Expansion             | 31 |

|              |     | 3.4.2 Gradual State Space Expansion                | 33 |

|              | 3.5 | Quantum Gates                                      | 35 |

|              |     | 3.5.1 Optimizing Quantum Gates                     | 35 |

|              | 3.6 | Error Analysis and Quantum Noise Modeling          | 38 |

|              |     | 3.6.1 Single Qubit Error                           | 39 |

|              |     | 3.6.2 Expanded State Space Error                   | 40 |

|              |     | 3.6.3 Gradual Word length Expansion                | 43 |

| 4            | Imp | plementation Details and Results                   | 45 |

|              | 4.1 | Software-based Gate Generator                      | 45 |

|              | 4.2 | Miscellaneous Architecture Components              | 47 |

|              | 4.3 | Emulator Mapping Results                           | 49 |

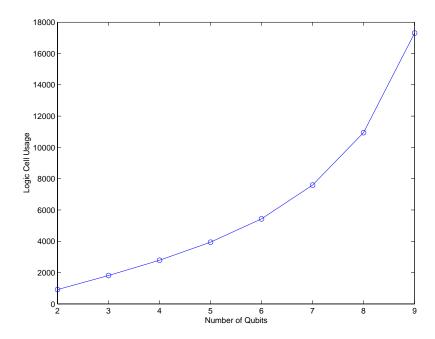

|              |     | 4.3.1 Synthesizing Quantum Circuits                | 50 |

|              |     | 4.3.2 Quantum Gate Synthesis Results               | 50 |

|              |     | 4.3.3 Expander Circuit Synthesis Results           | 52 |

|              | 4.4 | Computation Error                                  | 53 |

|              | 4.5 | Quantum Circuit Benchmarks                         | 54 |

|              | 4.6 | Scaling Quantum Circuit Emulation                  | 56 |

| 5            | Con | aclusion and Future Work                           | 58 |

|              | 5.1 | Thesis Summary                                     | 58 |

|              | 5.2 | Future Research Work                               | 60 |

| $\mathbf{A}$ | Qua | antum Measurement Simulation using Quantum Frames  | 61 |

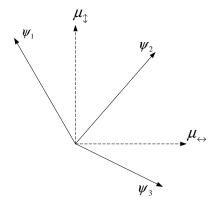

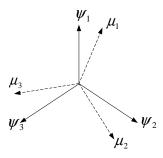

|              | A.1 | Quantum Measurement                                | 61 |

|              |     | A.1.1 Projective Measurements                      | 63 |

|              |     | A.1.2 POVM: Positive Operator-Valued Measure       | 63 |

|              | A.2 | Frame-Based Measurements                           | 63 |

|              |     | A.2.1 Distinguishing non-orthogonal quantum states | 63 |

|              |     | A.2.2 Least Squares Measurements and Tight Frames  | 65 |

| Contents                      |  |    |

|-------------------------------|--|----|

| A.3 Simulation of Measurement |  | 66 |

| A.4 Case Study                |  | 67 |

| References 7                  |  |    |

# List of Figures

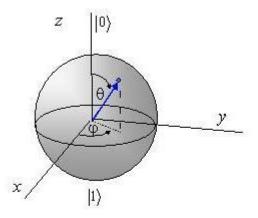

| 2.1  | Bloch Sphere                                                                   | 8  |

|------|--------------------------------------------------------------------------------|----|

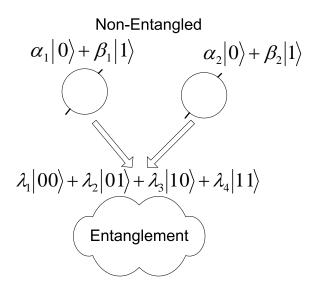

| 2.2  | Entanglement of two quantum particles                                          | 9  |

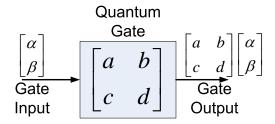

| 2.3  | Single-Input Quantum Gate                                                      | 10 |

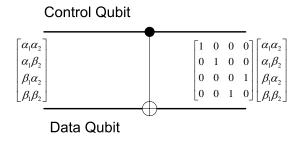

| 2.4  | 2-input CNOT gate                                                              | 12 |

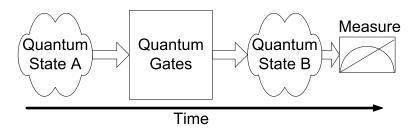

| 2.5  | Quantum computation as modeled by quantum circuits                             | 14 |

| 2.6  | The quantum Fourier transform circuit                                          | 15 |

| 2.7  | Three qubit Grover's search algorithm                                          | 15 |

| 2.8  | Oracles for the three qubit search algorithm                                   | 16 |

| 2.9  | Circuit simulation using QuCalc                                                | 17 |

| 2.10 | Vector description in QuIDDPro                                                 | 19 |

| 2.11 | Matrix multiplication example using QuIDDPro                                   | 19 |

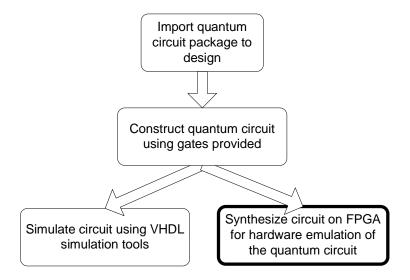

| 3.1  | Modeling quantum circuits using the VHDL quantum gate library                  | 24 |

| 3.2  | Emulation architecture overview                                                | 25 |

| 3.3  | Fixed-point quantum bit representation                                         | 26 |

| 3.4  | Two cases of state expansion: (a) Set of $n$ qubits (b) Two state spaces to be |    |

|      | expanded into a larger one                                                     | 29 |

| 3.5  | State space expansion using a ripple multiplier architecture                   | 32 |

| 3.6  | Gradual state space expansion                                                  | 33 |

| 3.7  | Gradual expansion of 3-qubit state space with two qubits already expanded      | 34 |

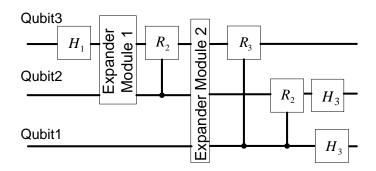

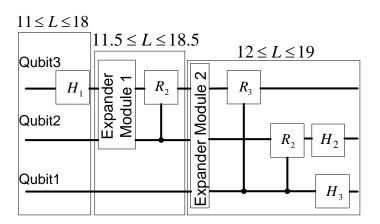

| 3.8  | 3-qubit QFT Circuit with expander modules                                      | 35 |

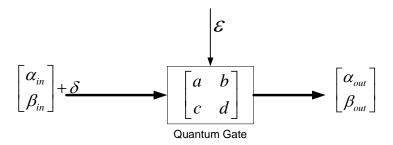

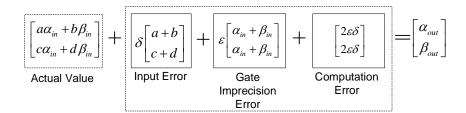

| 3.9  | Quantum gate error model                                                       | 39 |

| 3.10 | Expanded gate error model                                                      | 39 |

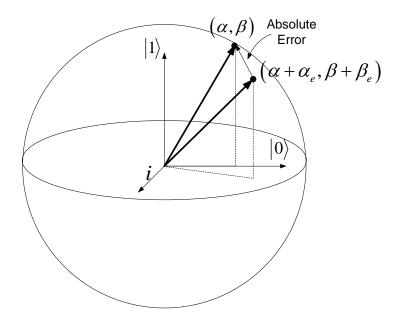

| 3.11 | Discretization error in a qubit                                                | 40 |

| 3.12 | Variation of word length with state expansion                                  | 44 |

| ist of Figures                                        | viii |

|-------------------------------------------------------|------|

|                                                       |      |

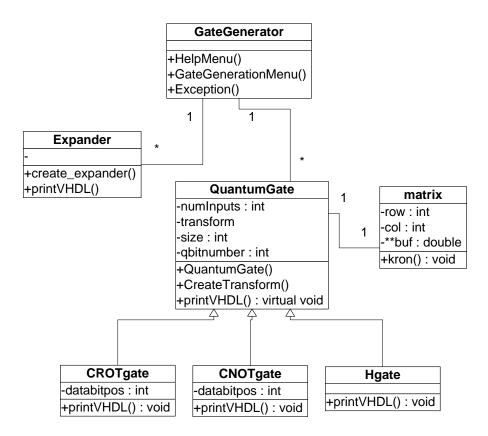

| 4.1 UML class diagram for the gate generator software | 46   |

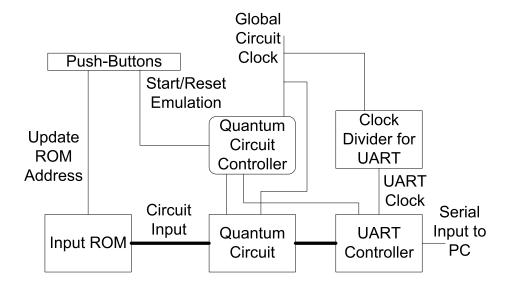

| 4.2 Block diagram of final emulation hardware         | 49   |

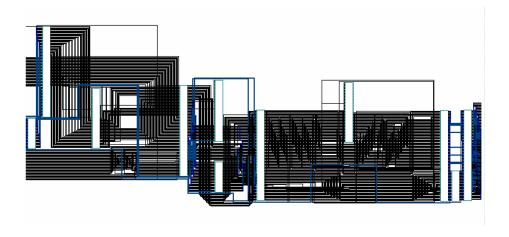

| 4.3 FPGA snapshot of the 3-qubit QFT circuit          | 50   |

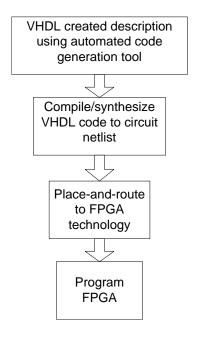

| 4.4 Quantum Circuit Emulator Synthesis Flow           | 51   |

| 4.5 Direct state space expansion circuit synthesis    | 53   |

|                                                       |      |

# List of Tables

| 4.1 | Logic Cell Usage on Altera Stratix EP1S80F1020C                  | 51 |

|-----|------------------------------------------------------------------|----|

| 4.2 | Comparison of the direct and gradual expansion techniques        | 53 |

| 4.3 | Error introduced by different gates for various mantissa lengths | 54 |

| 4.4 | QFT Benchmark                                                    | 55 |

| 4.5 | Grover's Search Algorithm Benchmark                              | 55 |

| A.1 | Measurement Probabilities for $\Psi$                             | 68 |

| A.2 | Measurement Probabilities for $\Psi_2$                           | 70 |

# Chapter 1

# Introduction

The new century has ushered in a spattering of new and innovative computational platforms that are envisaged to one day replace the currently prevalent semiconductor-based computers. Computation technology has spilled out of its traditional domains of electrical engineering and computer science into new realms such as quantum physics, biology and biomedical engineering. From storing information using the spin of photons to synthesizing transistors using organic molecules to performing large scale computation using DNA strands, researchers are moving towards the future of computing on many different roads. Research and development of these technologies is no longer limited to academic circles. Companies such as IBM, HP and D-Wave Sys are working towards bringing about the next revolution in computing in the not so distant future.

The focus of this thesis is on emulation of quantum computing. Quantum computing uses various quantum mechanical effects such as entanglement and superposition to provide massive performance speedup in certain types of computation problems such as data searching, factorization and encryption. The notion of using quantum mechanical phenomena for computational purposes was first explored in the the 1970's and early 1980's. Quantum computing came in to being when Richard Feynman proposed an abstract computational model for simulating quantum physics in 1982 [1]. This was followed by proposals by David Deutsch in 1985 of a general purpose quantum computer [2] and by Peter Shor in 1994 [3] where he proposed a factorization algorithm for quantum computers. It was Shor's publication that sparked widespread interest in quantum computing as it was the first large scale problem where quantum computers would outperform their classical counterparts

significantly.

Since then, the development of quantum technologies has been underway and a variety of different techniques are being considered to solve various hurdles facing quantum computing [4]. Some of the approaches being considered are:

- Collection of ions trapped and manipulated by lasers [5],

- NMR (Nuclear Magnetic Resonance) based information processing [6],

- Semi-conductor designs such as those based on quantum dots [7],

- Superconducting electronics [8].

Quantum computers however, are still in their infancy. The general unavailability of quantum computers has garnered interest in developing classical simulators of quantum algorithms. However, simulation of quantum algorithms presents its own set of challenges since simulating such phenomena in classical computers consumes an excessive amount of resources. This thesis proposes an FPGA-based solution to this problem, whereby parallel computation can be performed at a large scale in hardware resulting in significant performance gains as compared to software-based simulators.

# 1.1 Quantum Computation vs. Classical Computation

Quantum computation is an evolution of a quantum system that starts with a certain initial state. While the evolution of a quantum system can be described by a series of Schrodinger's equations [9], a more intuitive and equivalent abstraction of the quantum evolution is the quantum circuit model. The model breaks down the quantum system into two components: quantum bits which are the particles that make up the quantum system and quantum gates that are transforms that are applied on the collection of quantum bits. Therefore, analogous to classical computing quantum bits are the units of information and quantum gates are logical operations that can manipulate this information. However, unlike mainstream classical computation, quantum computation is probabilistic, that is the result of the computation cannot be achieved correctly in a finite number of steps. Furthermore, obtaining the state of the quantum system causes the system to collapse. At same time there is a significant probability of error in the obtained state information.

While classical units of information can exist in a finite number of states (predominantly binary logic is used where only the states 0 or 1 are present), quantum information can exist in an infinite number of states. Furthermore, quantum bits can undergo a quantum mechanical phenomenon known as *entanglement* whereby they can store an exponentially large amount of information. These effects can be employed to provide significant speed-up in computation in certain applications (such as data search and factorization).

### 1.2 Quantum Circuit Simulation vs. Emulation

Quantum circuit simulation involves numerical representation of the information stored in a quantum system and applying the necessary transforms on this information, as dictated by the quantum algorithm being simulated. The software-based simulators do not exploit the parallelism and the effect of quantum noise that are present in real-life quantum computers. Furthermore, since the state of the quantum circuits expands exponentially with linear increases in number of qubits, even a modest sized quantum circuit can take hours, even days to simulate.

The emulation of the quantum circuits also comprises of manipulating the mathematical representation of quantum information. However the goal is to replicate the behavior of the quantum algorithms when executed on a real quantum computer. This includes the effect quantum noise at the gate-level. While classical emulation of quantum circuits faces the same problems as in the case of simulation (i.e. significant growth in resource consumption) the added challenges are to perform computation in parallel and also recreate extrinsic factors such as quantum noise. Simulators have been developed that employ a programming language to describe quantum algorithms [10],[11] emulation requires that the quantum algorithm is described in terms of gates and quantum bits. Other simulators such as [12], [13] allow construction of quantum circuits using just gate interconnections, however they do not provide the level of performance as the description language-based simulators such as [10].

#### 1.2.1 Motivation for Emulation of Quantum Circuits

Quantum circuit emulation allows development of quantum algorithms in a more comprehensive manner as compared to simulation. Emulation goes beyond just mathematically

replicating a quantum algorithm but permits insight into more complex issues facing quantum computing such as quantum noise and quantum gate error. Furthermore, hardware-based emulation allows more control over the parameters of emulation such as word length of data-primitives as well as allows computational optimizations at the gate-level that are difficult to achieve in software. This in turn leads to a deeper understanding of issues facing classical modeling of quantum circuits. Finally, hardware-based emulation provides a significant performance improvement compared to software simulators.

#### 1.3 Thesis Contribution

This thesis proposes a gate-level FPGA-based solution to quantum circuit simulation. Using the analogues between the quantum and classical circuits, an emulation environment has been created where various issues such as quantum noise and parallel computation are taken into account. The emulator outperforms the premiere software simulators when considering algorithm runtime. Also combining classical error analysis techniques and relating them with quantum noise suffered by actual quantum computers, a bound on word length of data-primitives has been derived such that the emulated circuit produces results similar to those of a real quantum computer.

## 1.4 Thesis Organization

The rest of the thesis is organized as follows:

Chapter 2 provides a detailed background of the quantum circuit model including the different mathematical notations used to describe quantum computation. This is followed by an overview of different simulation techniques that have been developed for quantum circuit simulation.

Chapter 3 presents an in-depth look at the emulator architecture. Various challenges and hurdles were encountered in creating the emulation environment and details on how these challenges were over come are also presented. Finally, a thorough derivation of the word length bound is also presented.

Chapter 4 evaluates the performance of the performance of the FPGA emulator and compares it with other software simulators. A practical vindication to the theoretical work presented in Chapter 3 is also provided.

Lastly, Chapter 5 summarizes the work and presents the conclusion to the thesis. Directions for future work are also suggested.

# Chapter 2

# Background

The quantum circuit model provides an algorithmic abstraction for the quantum computation process. The model transforms the quantum physical phenomena that occur during the entire computation or "evolution" of the quantum system into lumped discrete events. A quantum system's time evolution that is normally represented using Schrodinger's equations (a collection of partial differential equations) is no longer required when using quantum circuits [9],[14]. Instead, the quantum information is represented as a state space (also referred to as a state vector) that depicts the state of the entire system at any given time. Evolution of states is then modeled using a collection of linear transforms that appropriately manipulate the state vector.

Information stored in a quantum system grows exponentially with the size of the system (number of quantum particles) [9],[14]. Manipulating the large state space with PDEs can be very resource-intensive for a simulator. Devolving the quantum computation into linear transforms does provide some reprieve for simulators, but for large state spaces they still have to perform a significant amount of computation. This will be clear after reading the following sections.

# 2.1 Quantum Bits

Quantum bits or *qubits* are the fundamental units of information in quantum computing. Analogous to classical computing, quantum computing is the manipulation of information stored in qubits. Physically, qubits have been realized using electrons, trapped ions and molecules. The information is stored using the spin or polarization of these particles. For

simulation purposes though, the state of the qubit is represented mathematically by a vector in a finite-dimensional complex Hilbert space [9]. The major property of the Hilbert space is that all vectors belonging to that space have a well-defined inner-product. For a vector f belonging to the Hilbert space, the norm of f is defined by

$$|f| = \sqrt{\langle f, f \rangle} \tag{2.1}$$

The *Dirac* bra-ket notation is a commonly used notation for denoting the state of the qubit. The notation is quite commonly used in quantum mechanics since it can conveniently represent the state of the system as well as describe operations on the system effectively. In the bra-ket notation, elements of H are "ket" vectors given by  $|x\rangle \in H$ . A corresponding "bra" vector  $\langle x|$  is an element of the dual space  $H^{*1}$ . For a quantum bit though the state  $|\psi\rangle$  of the bit is represented using the following equation

$$|\psi\rangle = \alpha|0\rangle + \beta|1\rangle \tag{2.2}$$

where  $\alpha$  and  $\beta$  are complex coefficients related by the following expression

$$|\alpha|^2 + |\beta|^2 = 1 \tag{2.3}$$

The  $|0\rangle$  and  $|1\rangle$  states of a qubit can be thought of as analogues to the classical bit. Physically,  $|0\rangle$  and  $|1\rangle$  states refer to a particular spin/polarity orientation of the qubit. However, as can be observed from Equation 2.2 and Equation 2.3, the qubit can simultaneously be in the both  $|0\rangle$  and  $|1\rangle$  states (an arbitrary spin/polarity). This phenomenon is known as *superposition* and is one of the fundamental sources of speed-up in quantum algorithms [9],[14]. Geometrically, a qubit can be thought of as a unit vector and can have any value on a unit sphere. Thus, a qubit can be in an infinite number of possible states. A common pictorial notation for qubits is known as the *Bloch sphere* and an example of that is depicted in Figure 2.1. Mathematically, Equation 2.2 can be re-written as Equation 2.4

$$|\psi\rangle = \cos\frac{\theta}{2}|0\rangle + e^{i\phi}\sin\frac{\theta}{2}|1\rangle$$

(2.4)

<sup>&</sup>lt;sup>1</sup>The  $\langle x|y\rangle$  notation is the inner product between the conjugate vector of x denoted as  $x^*$  and the vector y

Angles  $\theta$  and  $\phi$  are related to  $\alpha$  and  $\beta$  through a transformation from Cartesian to polar coordinates over complex number fields.

Fig. 2.1 Bloch Sphere

From a simulation point of view, only the values of  $\alpha$  and  $\beta$  need to be stored and manipulated as they represent the information stored by the qubit. Thus, a single qubit can be represented as a  $2\times1$  vector  $[\alpha \ \beta]^T$ . While the notation introduced so far is sufficient to describe the state of a single qubit, a more useful notation for representing the state of a n-qubit quantum system is as follows

$$|\Psi\rangle = |\psi_1..\psi_n\rangle = |\psi_1\rangle \otimes ... \otimes |\psi_n\rangle \tag{2.5}$$

where  $\otimes$  represents tensor product operation. The resulting state space  $\Psi$  is a  $2^n \times 1$  vector. This notation is useful as it collectively represents the state of the entire quantum system and assists in dealing with the computational interactions between the qubits themselves. The advantages of this representation will be encountered in the subsequent sections. However, an immediate disadvantage to this representation, from a simulation point of view, is that instead of dealing with 2n complex numbers for n qubits, the simulator now has to work with a state space of  $2^n$  complex numbers. This leads to an exponential increase in computation resource consumption.

### 2.2 Entanglement

Quantum entanglement is perhaps the most exotic quantum phenomenon used in quantum computing. Entanglement represents a situation when two or more distinct quantum particles behave in such a way that when one of the particles is subjected to change, a similar change is instantaneously applied to all the other entangled particles. Einstein, Podolsky and Rosen were the first to notice this effect in a pair of photons whereby the change in the spin of one photon resulted in the change of spin in the other simultaneously.

Fig. 2.2 Entanglement of two quantum particles

Mathematically, when a collection of qubits enters a state of entanglement, the notion of individual qubits disappears and the system can no longer be represented as a tensor product of individual qubit state vectors. In the case of n entangled qubits, the state of the system can only be represented using a  $2^n \times 1$  vector. Thus, it becomes necessary to represent the quantum system in the expanded notation described in the previous section. For an entangled system, the computational basis states also grow exponentially. While for single qubits the computational basis states were just  $|0\rangle$  and  $|1\rangle$ , for a two qubit entangled system the number of basis states expand to four:  $|00\rangle$ ,  $|01\rangle$ ,  $|10\rangle$  and  $|11\rangle$ . However, for entanglement to occur the system can only be in a superposition of the  $|00\rangle$  and  $|11\rangle$  or  $|01\rangle$  and  $|10\rangle$  states. In other superposition scenarios, the expanded state can be resolved into the tensor products of individual qubit states and hence the system can no longer said

to be entangled.

### 2.3 Quantum Gates

The quantum evolution of the system is modeled by applying a sequence of transformations on the quantum state space. The transformation or operations on the quantum system are called *quantum gates*. Classically, gates such as AND, OR and NOT are well known and any classical computation can be broken down into the operations these gates provide. In the quantum computation domain, all quantum algorithms can be broken down into constituent quantum gates that manipulate information and can deal with one or more units of information at one time (similar to multiple-input classical gates).

Mathematically, quantum gates can be represented as unitary matrices (operators) that can be applied to the state space or qubit vectors.

#### 2.3.1 Single Input Quantum Gates

Single input quantum gates are transformations that can operate on a single qubit in the system. Physically, these operations translate to altering the spin/polarity of quantum particle, thus changing the information stored by the particle. For instance, in the case of the trapped-ion implementation, the spin of the ion is changed using laser-ion interactions [5] and this operation can be modeled by a  $2 \times 2$  matrix.

Fig. 2.3 Single-Input Quantum Gate

One of the most important single qubit gates is known as the Hadamard gate or the H-qate. The H-gate transform is given as follows

$$H = \begin{bmatrix} \frac{1}{\sqrt{2}} & \frac{1}{\sqrt{2}} \\ \frac{1}{\sqrt{2}} & -\frac{1}{\sqrt{2}} \end{bmatrix}$$

The H-gate's importance is paramount in that this operation can be used to place qubits in a state of superposition from a  $|0\rangle$  or  $|1\rangle$  states. As described in the subsequent sections, many quantum algorithms achieve their speed-up due to the fact that they can operate on multiple quantum states (achieved through superposition) in parallel. Physically, a collection of quantum particles can be prepared in a known state of spins/polarities and the particles are then subjected to the Hadamard transform in order to place them in superposition.

Other common single input gates are the phase rotation gates that can alter the rotation of the qubit by an angle of  $\theta$ , the quantum NOT or X-gate that swaps the value of  $\alpha$  and  $\beta$  of a qubit and the Z-gate that flips the sign of the  $\beta$  value of the qubit.

$$Rot(\theta) = \begin{bmatrix} 1 & 0 \\ 0 & e^{i\theta} \end{bmatrix} \quad X = \begin{bmatrix} 0 & 1 \\ 1 & 0 \end{bmatrix} \quad Z = \begin{bmatrix} 1 & 0 \\ 0 & -1 \end{bmatrix}$$

However, single qubit operations are represented differently when using the expanded state space notation to represent the quantum system. For a n qubit quantum system, each gate operation has to be represented by a  $2^n \times 2^n$  sized matrix. This matrix is unique based on the basic operation that the gate performs and the position of the qubit. To elaborate, for a 3 qubit quantum system, if the H-gate is to be applied to the second qubit at any time the matrix representation would be calculated by performing  $I \otimes H \otimes I$  operation. If the same operation had to be applied on the third qubit instead, the resulting matrix representation would be performed using  $I \otimes I \otimes H$  and these two operations result in two different matrices.

From a simulation point of view, the process of applying these operations on a state space becomes exceedingly resource intensive as the size of these matrices grows exponentially. While most of the quantum gates result in sparse matrices, the sheer size of the matrices itself causes significant problems in simulating large quantum systems.

#### 2.3.2 Multiple Input Quantum Gates

Multiple input quantum gates perform an operation on an input qubit based on the value of the other inputs to the gate. Thus, multiple input quantum gates are controlled operation gates, where the value of the control qubits determines the gates' operation on the data qubit. A special type of multiple input quantum gate is the "swap" gate that swaps the information stored in two qubits.

Fig. 2.4 2-input CNOT gate

The input to a multiple input quantum gate is mathematically the expanded representation of all the individual quantum states. Hence, a n input quantum gate's transform is represented by  $2^n \times 2^n$  matrix. One of the most important quantum gates is the *controlled-NOT gate* (CNOT). In the simplest case, a two-input CNOT gate is represented by the following matrix

$$CNOT = \left[ egin{array}{cccc} 1 & 0 & 0 & 0 \ 0 & 1 & 0 & 0 \ 0 & 0 & 0 & 1 \ 0 & 0 & 1 & 0 \end{array}

ight]$$

Basically, if the control qubit is in the  $|1\rangle$  state, the gate swaps the  $\alpha$  and  $\beta$  values of the data qubit. However, if the control qubit is in the state  $|0\rangle$  the inputs are left unchanged. While this description of the gate's behavior works for the case where the control qubit is not in superposition, it fails to describe the behavior of the gate in the situation when the control qubit is in superposition. The behavior of the gate is expressed fully however, by the above matrix that operates on the expanded state space. No decision making is involved and the operation of that gate in this case is to swap the third and fourth entries

of the input state vector. The CNOT gate is however special, because in the case where the control qubit is in superposition and the data qubit is not, the resulting output is entangled. This can be understood by carefully examining the CNOT transform and a similar scenario can be created for generalization of CNOT gates (Toffoli gates). Due to the superposition states of the inputs, the quantum CNOT gate is thus more complex to its classical counterpart as its behavior needs to be expressed using the expanded state space.

Multiple input gate transforms also have to be adjusted to deal with the expanded state space of the entire quantum system. Each gate transform depends on the position of the inputs and overall size of the quantum system. For controlled input gates, it is computed using the *base transform* which is, for example in the case of CNOT is the X-gate transform. Essentially, the control gate transform is constructed by performing the Kronecker product between the base transform and the identity matrix. The resulting control gate transform is then further expanded using the Kronecker product with the identity matrix to adjust its size such that it can be applied to the entire state space.

### 2.4 Quantum Measurement

Quantum computation is probabilistic. Classical probabilistic circuits output a probability distribution based on the inputs of the circuit, the network topology and the induced probability distribution of the gates in the network. Therefore, in probabilistic computing, the results of computation cannot be accurately determined every time the outputs are subjected to measurement. This leads to probability of error in the measurement. Conversely, deterministic circuits are such that the results of the computation can be measured without error. In classical computation, deterministic circuits are mainly used and measurement error is not considered.

The probabilistic nature of quantum computation, thus, differentiates it from classical computing significantly. Quantum algorithms have to be designed such that the results of the computation can be achieved with low measurement errors and often the computation has to be repeated a considerable number of times before the results can be measured with high enough probability. This advertently affects the performance of the algorithm. Furthermore, quantum measurement or the act of extracting information from a quantum system is an irreversible operation as it destroys the quantum system being measured.

An intuitive way of understanding quantum measurements is to think of them as a

collection of operators on the quantum system (irreversible operators) such that the state of each quantum can be distinguished with some probability. These operators are projection matrices that map information from the quantum to the classical domain with some measurement error. After measurement, the qubit loses superposition and is measured in either of the computational basis states. The choice of these operators and the complexity of the quantum system determine the resulting measurement errors.

In the simplest case of a single qubit system, the  $|\alpha|$  and  $|\beta|$  coefficients from Equation 2.3 represent the probability that the qubit will be measured as  $|0\rangle$  or  $|1\rangle$  state respectively. For larger systems, the problem of quantum measurement becomes more complex and have a fundamental impact in quantum algorithm performance. In Appendix A, more details about simulation and optimization of quantum measurements are provided.

### 2.5 Quantum Algorithms as Quantum Circuits

Quantum circuits are a collection of wires (qubits) and gates that depict the time evolution of a quantum algorithm. The qubits are prepared in a known state and introduced as inputs to the system. The qubits then undergo evolution depicted by the gate operations on them. The evolution ends when the system is subjected to a quantum measurement. A number of quantum algorithms have been developed in the recent few years and they have sparked great interest in the field. In this section, an overview of two of the most famous quantum algorithms is provided.

Fig. 2.5 Quantum computation as modeled by quantum circuits

#### 2.5.1 Quantum Fourier Transform

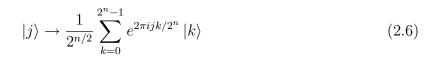

The quantum Fourier transform (QFT) plays an important role in the phase-estimation algorithms and the Shor's factorization algorithm [15]. While the QFT itself does not provide

a speedup in performing the Fourier transform on quantum information, its importance in other quantum algorithms makes it an interesting case-study.

For a n qubit system in state  $|j\rangle$  is subjected to the QFT, the output is given by

Fig. 2.6 The quantum Fourier transform circuit

Figure 2.6, depicts the QFT circuit for a n sized quantum system. The  $R_k$  gates can be represented as follows

$$R_k \equiv \left[ \begin{array}{cc} 1 & 0 \\ 0 & e^{2\pi i/2^k} \end{array} \right]$$

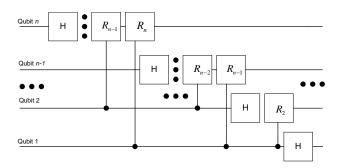

#### 2.5.2 Grover's Search Algorithm

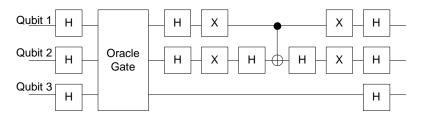

The Grover's search algorithm is the fastest search algorithm at the time of writing. It performs the search on a n sized database at the worst-case complexity of  $O(\sqrt{n})$  [16],[9] and can generally speed-up many classical algorithms that use searching or route-finding techniques. Figure 2.7, illustrates a 3 qubit Grover's search algorithm.

Fig. 2.7 Three qubit Grover's search algorithm

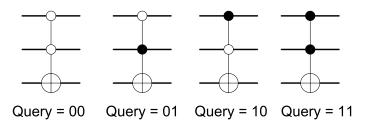

The oracle shown in Figure 2.7 is responsible for providing the answer to the search query. If the query is present in the first n qubits, then the Oracle sets the oracle qubit to  $|1\rangle$  state, otherwise the qubit is set to the  $|0\rangle$  state. The oracle itself can be constructed in this case using a CNOT gate with inputs according to the search query. Figure 2.8, shows the four different oracles for the three qubit Grover's circuit shown in Figure 2.7

Fig. 2.8 Oracles for the three qubit search algorithm

### 2.6 Software-based Simulation Techniques

In this section, a brief summary of three software-based simulators is given. The choice of the simulators is based on the fact that all three use very different simulation approaches. At the same time, they also represent the evolution of simulation techniques that have led to the development of the FPGA-based emulation technique. Quantum circuit simulators perform the mathematical operations of quantum gates on a given set of qubit states. The simulators are exclusively software-based.

#### 2.6.1 QuCalc: Mathematica Simulation Library

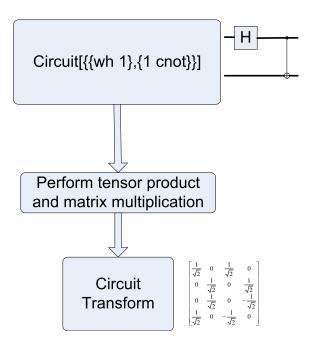

QuCalc is a simulation library written in Mathematica [13]. It makes use of the numerical and symbolic power of Mathematica to describe quantum circuits and simulate them. QuCalc uses the standard algebraic approach to simulate the quantum circuits. The gates making up the circuit are described symbolically as a multi-dimensional Mathematica array. The transforms of those gates are then concatenated together by perform matrix-matrix multiplication and tensor products to create an overall transformation of the circuit. This becomes the more computationally expensive part of the simulation. The circuit transform is a matrix that can then be applied to an input state vector. In Figure 2.9 a description of how QuCalc can be used to construct a circuit transform is provided.

Fig. 2.9 Circuit simulation using QuCalc

QuCalc is extremely straightforward to use, and construction of the circuits is very intuitive. The gate positions in the circuit can have a one-to-one mapping to their position in the array description in QuCalc. However, building very large circuits this way is very cumbersome and no mechanism is provided to facilitate that function.

In terms of performance, the simulator is limited by Mathematica as the simulation environment. As Mathematica is a symbolic computing package, a significant overhead is in the computation. While no specific benchmarks are provided for QuCalc, it is understood that its purpose is not to simulate large quantum circuits efficiently. QuCalc is a simple tool that can allow the construction of small to medium sized quantum circuits and provides a strong environment to algebraically and symbolically deal with issues pertinent to quantum circuits.

#### 2.6.2 QuIDDPro: An ADD based Simulation System

QuiDDPro is one of the fastest software simulators (at the time of writing) that is based on describing quantum transforms in terms of decision diagrams. The circuit is described using a Matlab-like programming language. QuiDDPro's novelty is that it represents the matrices and vectors that depict quantum transforms and quantum information as *Quantum*

Information Decision Diagrams or QuIDDs. A QuIDD is essentially an algebraic decision diagram (ADD), that have commonly been used to logically describe classical circuits [10], [17].

Since ADDs are designed to optimize binary logic circuits, the QuiDDs require additional properties to accommodate representing quantum information. First, unlike ADDs, a QuIDD's terminal nodes can have complex values (ADDs used for binary circuits can only have terminal values of 0 or 1). Secondly, in order to optimize operations on QuIDDs, the structure does not explicitly contain the complex values in the terminal nodes, but actually stores indices to an array that contains the actual terminal node values. This reduces computational overhead when performing operations on QuIDD-based vectors and matrices. Finally, the ordering of the nodes in QuIDD is such that it favors compression of block patterns in matrices. This optimization arises from the fact that the tensor product of quantum transforms produces highly regular block patterns. By ordering the nodes properly, the redundancy in the block patterns can be overcome and a smaller decision diagram can be used to describe the matrix.

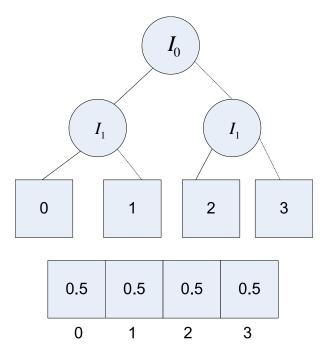

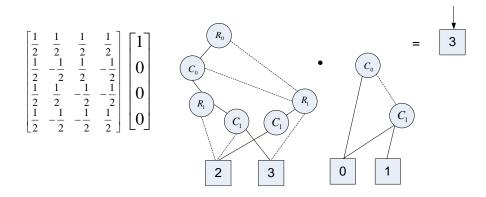

An illustration of how a QuIDD can store a vector representation of a quantum state is shown in Figure 2.10. Here it can be observed that a  $4 \times 1$  vector is represented using 3 nodes. A slightly involved QuIDD is used to describe the application of the Hadamard transform to a two-qubit vector as shown Figure 2.11. Here the left most QuIDD represents the Hadamard transform on a 2-qubit system. The next QuIDD represents the  $4 \times 1$  vector representing the 2-qubit system. The result of the multiplication can then be stored in just one terminal node.

While the information of the quantum circuit is stored using decision diagrams instead of regular matrices/vectors in QuIDDPro, the actual construction of the circuit transform and obtaining outputs is performed using tensor products and matrix multiplication as in the case of QuCalc. However, the advantage using QuIDD [10] is that the tensor product and matrix multiplication operations are quite efficient and having a reduced representation such as QuIDD can lead to significant performance gains. For matrices represented by nodes a and b, the tensor product comes out to be O(ab) while matrix multiplication is  $O((ab)^2)$ .

QuIDDPro has a Matlab like feel and can execute scripts written in a syntax similar to Matlab. It supports all necessary quantum transforms, however the construction of a quantum circuit is not immediately intuitive. Quantum algorithms are constructed using the functions provided in QuiDDPro in the form a programming language instead of a

Fig. 2.10 Vector description in QuIDDPro

Fig. 2.11 Matrix multiplication example using QuIDDPro

netlist. However, once the language issues are overcome, very large quantum circuits can be constructed quite easily. QuiDDPro's creators have provided detailed runtime performance of the system when simulating the Grover's search algorithm. From [10], QuIDDPro can simulate the Grover's search algorithm with a memory complexity of O(n) and time complexity of  $O(R|A|^{16}n^{14})$  where R is the number iterations of the algorithm, A is the number of nodes in the oracle representation and n is the number of qubits. Running times provided in [17] for the Grover's search algorithm are less than 6 minutes for simulating a 20 qubit circuit.

#### 2.6.3 HDL Based Simulation of Quantum Circuits

Simulation of quantum circuits using a hardware description language such as VHDL [18] has been proposed in [19]. This technique uses analogies between the quantum circuit model and classical circuits to construct and simulate the quantum circuits.

HDL simulation of quantum circuits diverges from the strongly algebraic approaches in the previous two simulators. As the quantum circuit model breaks down the quantum transform into quantum gates and quantum bits, the HDL approach can incorporate these architectures directly as they are congruent analogues to classical gates and bits respectively.

Qubits are described as two complex numbers (using the *real* keyword in VHDL). The gates are constructed with qubits as inputs and outputs and the transform of the gate is described using behavioral VHDL. The quantum circuit can be constructed now by combining the gates using structural VHDL.

However, the key issue here is entanglement. The previous two simulators dealt with the quantum circuit by expanding it to the full bases states and applying tensor products to achieve the final circuit transform. The expansion operation explicitly deals with entangled situations since the computational state space is already large enough to hold the entangled information. In the case of HDL simulation however, the goal is to describe the circuit in the simplest gates possible, and thus the presence or absence entanglement has to be explicitly detected and simulated. In [19], detailed entanglement extraction algorithms have been derived. They are able to detect when entanglement occurs or disappears. These are simulated using functional VHDL and have exponential complexity. This amounts to similar resource usage as in the case of expanded state space simulators.

Since the simulator uses VHDL to simulate quantum circuits, the CAD simulation tools available for the development of classical circuits using VHDL can now be employed to construct quantum circuits. This involves either using structural VHDL or a graphical netlist creation tool. In both situations, it is straightforward how to create the circuit and simulate the results.

According to [19], the runtime in the non-entangled case of simulation is  $O(n^2)$ . Some simulation runtimes are also quoted in [19] for small quantum circuits. However, entanglement extraction is still complex. Overall, the simulation would also be limited to the speed of the VHDL simulation tool.

# Chapter 3

# FPGA Emulator Design

This chapter provides details of the emulator design and design choices. The challenges involved in performing hardware emulation of quantum circuits are laid out. This is followed by a description of how these challenges were overcome.<sup>1</sup>

### 3.1 Challenges in Emulating Quantum Circuits

While the underlying principles of classical circuits are well understood, and have been widely applied, the same is not true for quantum circuits. So far, quantum circuits have been rarely demonstrated and in rather small sizes. Although existing quantum computing machines employ at most 7 qubits, even such a small number of qubits are notoriously hard to analyze and employ in concerted quantum machines.

Simulating quantum circuits in software is even more cumbersome than in the classical case. Currently available simulators like [19],[10] while providing an environment for the development of quantum algorithms, still greatly abstract the quantum evolution of the qubits. The speed of running a single simulation pass is even more critical than for classical circuits. Due to little understanding of hardware modeling of quantum processes, it is very likely that that many changes will need to be introduced to the model itself. This, in consequence, would lead to several re-runs of simulations of a given quantum design. Therefore emulators which perform fast simulations, and can be easily re-programmed to account for small changes in the model of quantum processes as well as the design itself are

<sup>&</sup>lt;sup>1</sup>Part of the work presented here has already been published in [20]

essential. Such capabilities can be provided by FPGA-based hardware emulators. Finally, using the quantum circuit model is a very intuitive way of constructing quantum algorithms and would greatly assist in the development of new algorithms. Thus, the emulator combines important quantum computing concepts and a solid development environment to serve as a development and test-bed for quantum algorithms.

The first and foremost problem with quantum circuit emulation, is the mapping of quantum computation concepts to the digital domain. While the quantum circuit model creates a classical analog for quantum computing, it still possesses appreciable differences from classical circuits. The goal is to efficiently describe quantum circuits using a classical hardware description language, such that the final circuit can be synthesized on a FPGA.

The second major challenge is to emulate the quantum circuit such that the resources available on the FPGA are used as efficiently as possible. Resource requirement becomes a serious issue with entangled systems as performing quantum evolution in a highly entangled system requires an exponential amount of computation. Emulating quantum circuits with FPGAs has an advantage that FPGAs have a large amount of logic cells (and multiple FPGAs can be combined for even bigger circuits) and therefore large quantum circuits with entangled states can be emulated easily and efficiently in terms of computation time.

Finally, the overall architecture should still emulate the parallel evolution of the quantum system as closely as possible since that is one of the main motivations for performing quantum circuit emulation in hardware. Thus, balancing the resource usage and parallelism in the emulator is an important design consideration.

#### 3.2 Emulation Overview

The overall design process is illustrated in Figure 3.1. Quantum circuits are constructed from the quantum gate descriptions that are part of the emulator. The correctness of the circuit can be verified either by software simulation or by FPGA emulation. Thus, a technique has been developed for modeling quantum circuits using VHDL and then synthesizing the circuit in hardware to achieve performance needed to make the whole process more practical.

The emulator comprises of two major components. The first is a C++ based commandline interface that has been created and is used to generate VHDL description of the gates required in the quantum circuit. The interface allows a fast way of calling the C++ based

Fig. 3.1 Modeling quantum circuits using the VHDL quantum gate library

functions that generate gate descriptions for gates such as the X-gate, Z-gate, Hadamard Gate, Rotation gates and common multiple input gates such as the controlled version of the single input gates and the swap gate. The interface requires the user to enter the gate name, system size and number of inputs and it then generates the appropriate VHDL description of the gate. All the gates created from the interface use the expanded state space notation for inputs and outputs. More details about the developed software are provided in the subsequent sections.

The second part of the emulation environment are the data primitives defined in VHDL and the final circuit structural description. The data primitives are used to define complex number-based entities such as the qubit state vectors and the expanded state space notation. While all the gate descriptions can be generated via the software component of the emulator, the final quantum circuit model has to be created by either using structural VHDL or a schematic environment such as the one present in Altera's Quartus II software.

The emulator's architecture overview is illustrated in Figure 3.2. Emulator circuitry on the FPGA closely follows the quantum circuit topology as a series of gates are applied to the qubits on the FPGA in the same order as the quantum circuit itself. However, at certain places in the quantum circuit a register is inserted and this sequence of registers allows the pipelining [21] of the entire computation. All these registers are controlled by a single global clock and the speed of the clock depends on the slowest stage [21] of the

Fig. 3.2 Emulation architecture overview

quantum circuit pipeline. The registers store the state of the quantum system at a given point and time of the quantum evolution. The clock serves to synchronize the computation and can be used to determine the total computation time.

Furthermore, the pipelined architecture allows the quantum circuit to be quickly simulated for multiple inputs thus providing a significant advantage over software simulators where the circuit has to be re-simulated for each set of inputs. Finally, at the end of the computation the final state of the quantum system is transmitted from the FPGA to a PC. Details about each component of the architecture are provided in the following sections.

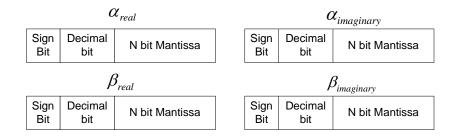

## 3.3 Data primitives

The first step in creating the emulator is to develop a mechanism for representing quantum information digitally using VHDL. From Equation 2.2, the information of the qubit is stored in two complex numbers  $\alpha$  and  $\beta$ . In VHDL, there are no native data primitives to deal with real numbers (floating or fixed point). Thus, the choice that had to be made was to represent the complex numbers using floating point or fixed point schemes. Initially, a floating point representation was considered but it was discarded because the emulator would have to perform considerable amount of floating point operations and it would be very resource consuming to have many floating point adders or multipliers in hardware. An architecture based on hardware reuse was also considered but that reduced the parallelism

in the emulator significantly.

The other choice was to develop a fixed point scheme for representing the real and imaginary parts of the complex numbers. The fixed point scheme yielded less arithmetic overhead at the cost of lower precision. Figure 3.3 depicts the fixed-point representation that was chosen for the emulator. There are two salient features of this representation

- 1. According to Equation 2.3,  $|\alpha|$  and  $|\beta|$  can have a maximum value of 1. Therefore, an extra bit is used in the representation scheme (the second most significant bit) to represent the case where the  $\alpha$  or  $\beta$  have a value of 1 or i unambiguously and without discretization errors.

- 2. The length of the mantissa bit can be varied. The size of the data primitives has a direct relationship with the amount of resources (logic cells or LCs) consumed on the FPGA; the designer has the ability to trade-off resource usage against precision.

Fig. 3.3 Fixed-point quantum bit representation

Having a variable sized mantissa allows a certain amount of flexibility to the emulator. Depending on circuit size, precision requirements and available resources, the synthesized quantum circuits can be "tuned" to fit these parameters. It also opens the avenue for experimenting with circuit precision and modeling quantum noise that are difficult to perform with software simulators. In [22],[23] quantum noise simulation has been suggested and later in this chapter more details about error analysis and quantum noise simulation are provided.

The following code enlists all the data primitives in VHDL. Notice that in order to vary the system precision, only the value of the constant N is changed and the circuit is recompiled.

```

LIBRARY ieee;

USE ieee.std_logic_1164.all;

PACKAGE quRecords IS

CONSTANT N

: INTEGER := 10;

TYPE complexNum IS RECORD

: STD LOGIC VECTOR(N-1 downto 0):

real

: STD_LOGIC_VECTOR(N-1 downto 0);

imaginary

END RECORD;

TYPE quBit IS RECORD

alpha

: complexNum;

: complexNum;

beta

END RECORD;

TYPE complexArray IS ARRAY (integer range <>) OF complexNum;

TYPE entangledQubit IS ARRAY (integer range <>) OF complexNum;

TYPE quArray IS ARRAY (integer range <>) OF quBit;

TYPE result IS array (integer range <>) of std_logic_vector(twoN-1 downto 0);

END quRecords;

```

#### 3.3.1 Emulation of the expanded state space

As described in Chapter 2, due to entanglement, single-qubit evolution is not sufficient to describe quantum computation. The same fixed point scheme is used to represent the complex numbers in the expanded state space representation. However, expanding the state space causes an exponential growth in resources. Thus, the quantum circuit has to be synthesized such that the state space is expanded only when absolutely necessary. Originally, quantum emulation begins with the the inputs represented as initial values of the qubits. The expanded state space notation is introduced when a multiple-input quantum gate is encountered. If a qubit, already in an expanded state space, is an input to a multiple input gate, the other input qubits are included in the state space of the originally expanded state. In the case where multiple expanded state spaces are inputs to a quantum gate, the inputs are combined into a larger state space just as the in the second situation for state space expansion.

# 3.4 Expander Circuits

As shown in Chapter 2, state space expansion is a necessary operation during the emulation of quantum evolution. The two primary reasons for the inevitability of the use of this notation are:

- Entanglement situations can only be represented using a single vector using the state space expansion technique,

- The mathematical operation of multiple-input quantum gates is directly applicable to the expanded state vector.

The state space operation is essentially the implementation of the operation defined in Equation 3.1.

$$\bigotimes_{i=1}^{n} |\psi\rangle = |\psi_1\rangle \otimes |\psi_2\rangle .. \otimes |\psi_n\rangle \tag{3.1}$$

where  $|\psi_i\rangle$  can either be a qubit state vector or an expanded state vector. In terms of a general classical simulator, the state expansion operation presents two challenges:

- Implementation of the Kronecker product operations Equation 3.1 as a large amount of complex multiplications have to be performed,

- Emulation of expanded gate transforms that have to operate on the expanded state.

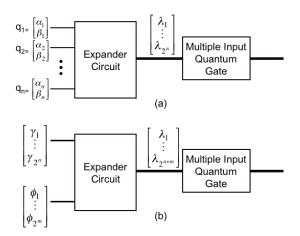

There are two scenarios of state space expansion: one from a set of qubits, and the second from a combination of state spaces. In the first case, the state space is expanded directly to its maximum size  $(2^n$  for an n qubit system). This operation requires  $(n-1) \times 2^n$  complex multiplications to implement. Figure 3.4(a) describes the situation for state expansion from a set of qubits. Each  $\lambda_i$  is computed by cycling through all the combination of  $\alpha$  and  $\beta$  values of each of the n qubits. Therefore, n-1 complex multiplications are performed for each of the  $2^n$  entries of the expanded vector.

The second case allows the state space to be gradually expanded in consequence, a larger state space can be constructed by combining several smaller states. When combining a vector of size  $2^m$  with another vector of size  $2^n$ , the total number of complex multiplications required is  $2^{m+n}$ . Figure 3.4(b) depicts the situation where two state vectors  $\gamma$  and  $\phi$  are

**Fig. 3.4** Two cases of state expansion: (a) Set of n qubits (b) Two state spaces to be expanded into a larger one

expanded into a larger vector  $\lambda$ . Each of the  $2^m$  entries of the  $\lambda$  vector are computed by multiplying each element of the  $\gamma$  vector by the entire  $\phi$  vector.

The computational complexity is further exacerbated when even single qubit quantum gates have to be expanded so that they can operate on the expanded state space. Software simulators such as [13],[10] approach the problem by expanding the state-space at the beginning of the computation. In consequence, the rest of the computation involves operations on large matrices. Techniques involving the use of decision diagrams to reduce the complexity of the computation have been employed [10]; however operations on large circuits still require considerable time and memory usage.

State space expansion for purposes of FPGA emulation presents bigger challenges than those faced by any general classical simulator of quantum circuits. In essence, the FPGA emulator performs computation in parallel (by executing concurrent parts of the algorithm at the same time), thus mimicking quantum parallelism and gaining a significant speed-up over software simulators. Quantum gate transform matrices are normally sparse (in most cases diagonal or quasi-diagonal where a significant number of non-zero entries are equal to one and hence require no actual complex multiplication). Therefore, they are mapped to hardware directly, and operate on the input state space in a non-sequential way. However, this design strategy becomes imprudent and impractical when performing the state space expansion operation for even a small number of qubits. The complex multipliers needed to implement directly 3.1 consume an enormous amount of resources on the FPGA (in terms

of logic cells), and become impossible to synthesize beyond a modest number of input qubits.

Additionally, the expanded state space emulation also causes the quantum gate implementation to consume more resources. It is possible to re-factorize an expanded state space into smaller state vectors in the case where no entanglement is present. However it has been shown in [19] that the detection of the non-entanglement condition and factorization of the expanded state space require an exponential amount of computations themselves, and is non-synthesizable in hardware.

A further constraint on the state space expansion operation is imposed by the fact that it has to be completed within one pipeline stage (or split over several pipeline stages). In consequence, a sequential operation within a pipelined architecture has to be performed. In order to keep the circuitry straight-forward, the clock used in the sequential operation has to be in phase with the global clock of the pipeline registers. Therefore, the global clock cycle has to be long enough for the operation to complete, possibly augmenting with increasingly sequential implementations of the state space expansion operations. This in turn extends the overall computation time. The following inequality must hold true for the proposed architecture to operate correctly:

$$clock_{global} \ge M \times clock_{exp}$$

(3.2)

where M is the number of sequential operations needed to be performed for state space expansion, and  $clock_{exp}$  is the period of the clock driving the expander circuitry.

There are multitudes of ways in which the expansion operation can be realized in hardware. Using more complex multipliers in the expander circuit reduces the number of sequential operations (M), hence a faster global clock can be used. The disadvantage of this approach is the increase in the resource usage of the expander circuit. The benefit of having a smaller  $clock_{global}$  to  $clock_{exp}$  ratio is that built-in clock multipliers on the FPGA can be used to obtain  $clock_{exp}$  without actually slowing down the global clock. Depending on the size of M in Equation 3.2 and the clocking capacity of the FPGA, the expander clock is obtained by multiplying the global clock by M. Therefore, for a fraction of the resources that would be consumed if the state space expansion was to be performed non-sequentially, the sequential approach incurs no penalty in terms of computation time.

Finally, for an arbitrary sized quantum circuit, the architecture of the expander needs to be scalable and parametrizable, since its description has to be generated in software, just as in the case of quantum gates. The design philosophy is thus to design an architecture for the expander circuits such that they perform their tasks in a sequential manner, while balancing the resource usage on the FPGA and the overall performance of the quantum circuit. Furthermore, the state space is also expanded only when necessary (in the case where multiple-input quantum gates are encountered). Therefore, unlike software simulators, the state space is expanded gradually whenever possible and smaller representations for quantum gates are used when possible.

#### 3.4.1 Sequential State Space Expansion

The expansion operation can be implemented sequentially in several ways. First consider an element that can be used to obtain the expanded state space from a set of qubits. Such a circuit would be useful when the qubits are subjected to multiple input quantum gates, Figure 3.4(a). The range of solutions is a function of the number of multipliers used to realize the operation in Figure 3.4(a). In the simplest case a multiply-accumulate (MAC) loop is suitable to handle this task, requiring a clock ratio  $clock_{global}/clock_{exp} = (n-1) \times 2^n$  to expand n qubits. The resulting slow down of the global clock is significant even for modest n.

A more favorable solution from the perspective of the FPGA emulator is the one implementing the sequential operation using a ripple multiplier architecture. It was noted that the expansion operation from 3.1, can be broken down into  $2^n$  sequential steps using n-1 multipliers in a ripple configuration instead of just one in the case of the MAC. Note that n-1 multipliers are needed since each entry of the expanded state vector is computed by performing n-1 complex multiplications between n complex numbers, which are the  $\alpha$  or  $\beta$  values of the n qubits. The output state vector is formed from the  $2^n$  possible combination of these values.

The algorithm depicted in Figure 3.5 depicts the operation of the ripple multiplier expander circuit. A *count* variable is used to cycle through all the possible combinations of  $\alpha$  and  $\beta$  of the input qubits stored in a single dimension array *qubitarray*. Each combination of the complex values is then sent to the ripple multiplier architecture (lines 12 to 14) and the resulting output is stored in the expanded output vector *outstate* indexed by the *count*

variable. With this architecture, the  $clock_{global}$  to  $clock_{exp}$  ratio is  $2^n$ , which is a significant improvement from the MAC architecture. Furthermore, it is straightforward to design a scalable version of this architecture (to be generated via software) that is parametric on the number n of input qubits. The major issue with the ripple multiplier architecture is a difficulty with its synthesis due to the large logic cone from inputs to outputs. The synthesizer (Leonardo Spectrum running on a PC with 2GB of memory) quickly runs out of memory when synthesizing the expander circuit for more than 9 input qubits. However, at the system level, it is noted that the majority of quantum circuits comprise of single-to three-input quantum gates. Therefore, this architecture can be used for expanding the state space for two to three qubits without any synthesis problem. Since the qubit state vectors have to be expanded when subjected to a multiple-input quantum gate, only two or three qubit expansions need to be performed in most cases.

```

1. expand_direct(start_vec,end_vec,n,qubitarray)

3. // expansion of vector qubitarray

4. // expanded state stored in outstate

count := 0

while (count not equal 2^n -1) {

7.

for i = 0 to n-1

8.

if (count(i) equals 0)

9.

out_count(i) := qubitarray(i).alpha

10.

11.

out_count(i) := qubitarray(i).beta

12.

out_mult := out_cont(0) * out_cont(1)

13.

for i = 1 to n-1

out_mult := out_mult * out_cont(i)

14.

15.

outstate(count) := out_mult

16.

count := count++

17.

18.}

```

Fig. 3.5 State space expansion using a ripple multiplier architecture

The proposed architecture, however, is not suitable to cover all these cases where expanded inputs are inputs to a multiple-input quantum gate (Figure 3.4(b)) or when a large quantum gate is encountered (in the case of an oracle circuit [9]). Another expander circuit architecture is therefore needed that can be used to combine expanded state spaces together to form a larger state space. To achieve these goals the gradual state space expansion architecture is proposed that has the ability to combine smaller state vectors into larger ones. Thus, the final state vector is obtained by performing multiple expansions.

## 3.4.2 Gradual State Space Expansion

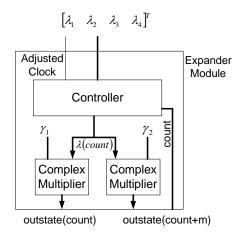

The gradual state space expansion architecture faces similar design constraints as the expander architecture described above. The operation of this architecture is also sequential as this expansion requires a significant amount of complex multiplications. Therefore, the goal is still to find an optimal balance between resource usage and overall computation time, while at the same time have a scalable and parametric architecture.

```

1. expand_grad(state1,state2,m,n, outstate)

2. {

3. // state1 of length m and state2 of length n are

4. // combined to form a larger state vector outstate

5. count := 0

6. while (count not equal m-1) {

7. out_cont := state1(count)

8. count := count++

9. for k = 0 to n-1 {

10. out_mult(k) := out_cont* state2(k)

11. outstate(count + k*m) := out_mult(k)

12. }

13. }

14. }

```

Fig. 3.6 Gradual state space expansion

The expander circuit takes two state space vectors as inputs as shown in Figure 3.4(b). One of the state space vectors can be simply a  $2 \times 1$  qubit state vector. For example, consider a situation where  $state_1 = [\lambda_1...\lambda_m]$  and  $state_2 = [\gamma_1...\gamma_n]$  are the input vectors to the expander circuit. The algorithm in Figure 3.6 illustrates the steps for the gradual state space expansion. The controller again comprises of a counter *count* (lines 5 to 10) that is used to cycle through all elements of the state vector with length m. Then n complex multipliers, each with one entry from the  $state_2$  vector, compute n entries of the output state vector (lines 12 and 13). The operation of the circuit can be summarized as:  $outstate(count + k \times m) = \gamma_k \lambda_{count}$ , where  $k \in \langle 0, n-1 \rangle$ . Figure 3.7 illustrates the architecture of gradual state space expansion example where a two qubit expanded state space is combined with a third qubit (m = 4 and n = 2).

The choice of the number of multipliers used in this architecture is determined experimentally based on observing various quantum circuit topologies at the system level. In many cases such as the quantum Fourier transform (QFT) [9], adder [24] and Grover's oracle circuits [16], a large state vector combines with a smaller state. The tradeoff be-

**Fig. 3.7** Gradual expansion of 3-qubit state space with two qubits already expanded

tween resource constraints and circuit performance leads to two choices. One represents a fast design, with the number of multipliers equaling the length of larger state vector ( $\gamma$  in Figure 3.4(b)). In the alternative approach, the saving of the resources is obtained through the use of a smaller number of multipliers that equal the length of the smaller state vector ( $\phi$  in Figure 1(b)).

The proposed architectures allow performing the expansion within a pipeline stage efficiently in terms of resources consumed on the FPGA and the penalty in overall computation time. It is scalable and parametrizable, thus satisfying all the requirements of the expansion circuitry. The major advantage of the proposed expansion techniques is seen at the system level. The notion of a gradual state space expansion provides considerable improvement in the performance of the emulator for many topologies such as the QFT and quantum adder circuits.

Figure 3.8 depicts the 3-qubit QFT circuit that uses the proposed state space expansion technique (the expander modules 1 and 2 are implementations of algorithms depicted in Figure 3.5 and 3.6 respectively). In this example, the state space is expanded in two stages permitting Hadamard (H1) and rotation (R2) gates to operate on smaller state spaces, thus saving a considerable amount of resources.

Fig. 3.8 3-qubit QFT Circuit with expander modules

# 3.5 Quantum Gates

In this section details about the optimization and design decisions with regards to the emulation of quantum gates are provided. An in-depth analysis of the design of three important quantum gates is undertaken in this section.

# 3.5.1 Optimizing Quantum Gates

The basic single input quantum gate descriptions can be easily created using the data primitives defined previously. Instead of performing matrix multiplication with the input state vector, the gates are designed such that they make use of the matrix structure and only the necessary complex multiplications are synthesized. For gates such as the X-gate or CNOT gate, the matrix elements are only 0 and 1. Furthermore, there is only one non-zero element in each row of the matrix. These gates can then be implemented without any complex multiplications since they simply swap elements in the state vector. The swaps can be performed by using simple structural VHDL commands. On the other hand, the Hadamard gate has a full matrix description and in this case the matrix multiplication is inevitable.

However, when these gates are applied to the expanded state space vector, the matrix descriptions are large  $(2^n \times 2^n)$  for a n-sized system) and usually sparse. Thus, it becomes necessary to implement the gates' operation on the state vector using the matrix structure and minimizing the number of complex multiplications. The following three case studies look at the implementation of the H-gate, CNOT gate and the controlled rotation gates to further illustrate the implementation of different gate architectures on the FPGA. It is

important to illustrate the implementation of these gates in detail since it would help to justify the performance analysis of the emulator presented in Chapter 4.

#### Emulation of the CNOT Gate

In the expanded state space notation, the CNOT gate has a similar matrix structure as that of a single input NOT gate albeit at a larger scale. The matrix describing a 3 qubit generalization of the CNOT gate (Toffoli gate) where the NOT operation is applied to the third qubit is as follows:

$$CNOT_{pos3size3}( heta) = egin{bmatrix} 1 & 0 & 0 & 0 & 0 & 0 & 0 & 0 \ 0 & 1 & 0 & 0 & 0 & 0 & 0 \ 0 & 0 & 1 & 0 & 0 & 0 & 0 \ 0 & 0 & 0 & 1 & 0 & 0 & 0 \ 0 & 0 & 0 & 0 & 1 & 0 & 0 \ 0 & 0 & 0 & 0 & 0 & 0 & 1 \ 0 & 0 & 0 & 0 & 0 & 0 & 1 & 0 \end{bmatrix}$$

As can be observed from the above matrix, the operation of the CNOT gate can be implemented by performing a simple swap of the seventh and eighth entries of the input state vector. The following code illustrates this optimization:

```

USE WORK.QURECORDS.ALL;

ENTITY CNOTGATE3posOnuminput3 IS

PORT(

input : IN entangledQubit(7 downto 0);

output : OUT entangledQubit(7 downto 0)

):

END CNOTGATE3posOnuminput3;

ARCHITECTURE CNOTGATE3_structural OF CNOTGATE3posOnuminput3 IS

BEGIN

output(0) <= input(0);</pre>

output(1) <= input(1);</pre>

output(2) <= input(2);</pre>

output(3) <= input(3);</pre>

output(4) <= input(4);</pre>

output(5) <= input(5);</pre>

output(7) <= input(6);</pre>

```

```

output(6) <= input(7);

END CNOTGATE3_structural;

```